As software-defined vehicles shift from concept to scale, the flaws of traditional distributed architectures are becoming glaring. Scattered layouts involving dozens or even hundreds of ECUs have created high complexity, data silos across domains, and hurdles in deploying AI functions—bottlenecks constraining the industry's upgrade.

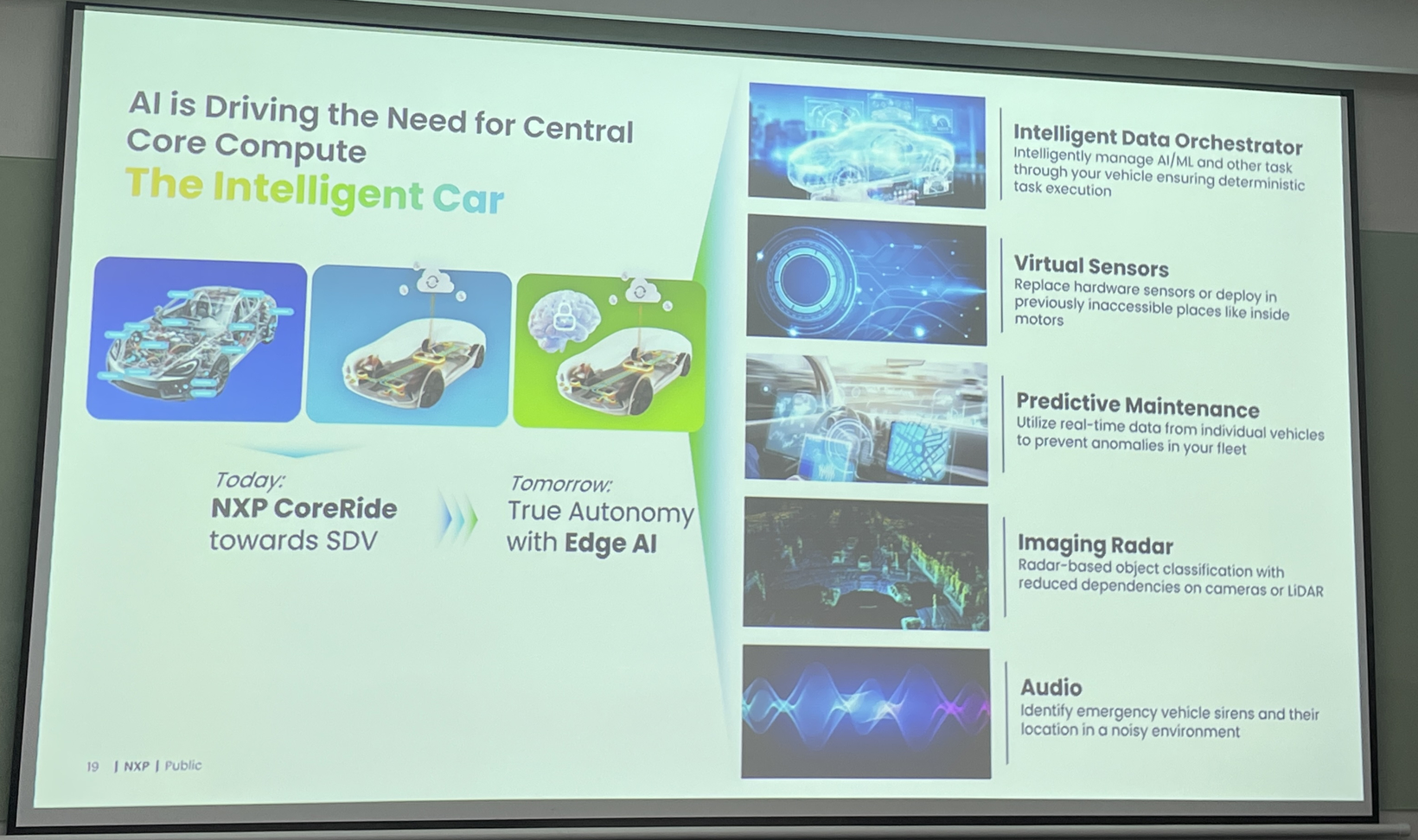

Against this backdrop, the emergence of high-integration central computing processors is driving a critical leap in automotive electronic/electrical (E/E) architectures—from "distributed domain control" to "central computing"—reshaping the competitive landscape.

From Scattered to Centralized: The Core Logic to Solving Industry Pain Points

"Vehicles today are becoming increasingly complex, with more features embedded. Consumers expect the latest technology, feature updates, and even personalization. But in hardware-defined vehicles, changing a single function might require adjusting 10 ECUs and 50 software modules—a massive challenge for automakers," Jens Hinrichsen, executive vice president and general manager of analog and automotive embedded systems at NXP Semiconductors, stated bluntly at a recent media briefing.

He pointed out that automakers must therefore drive vehicle digitization, decoupling functions from hardware and implementing them through software. This allows feature updates to be completed quickly via a central computer—but it requires a powerful in-vehicle computing platform as support.

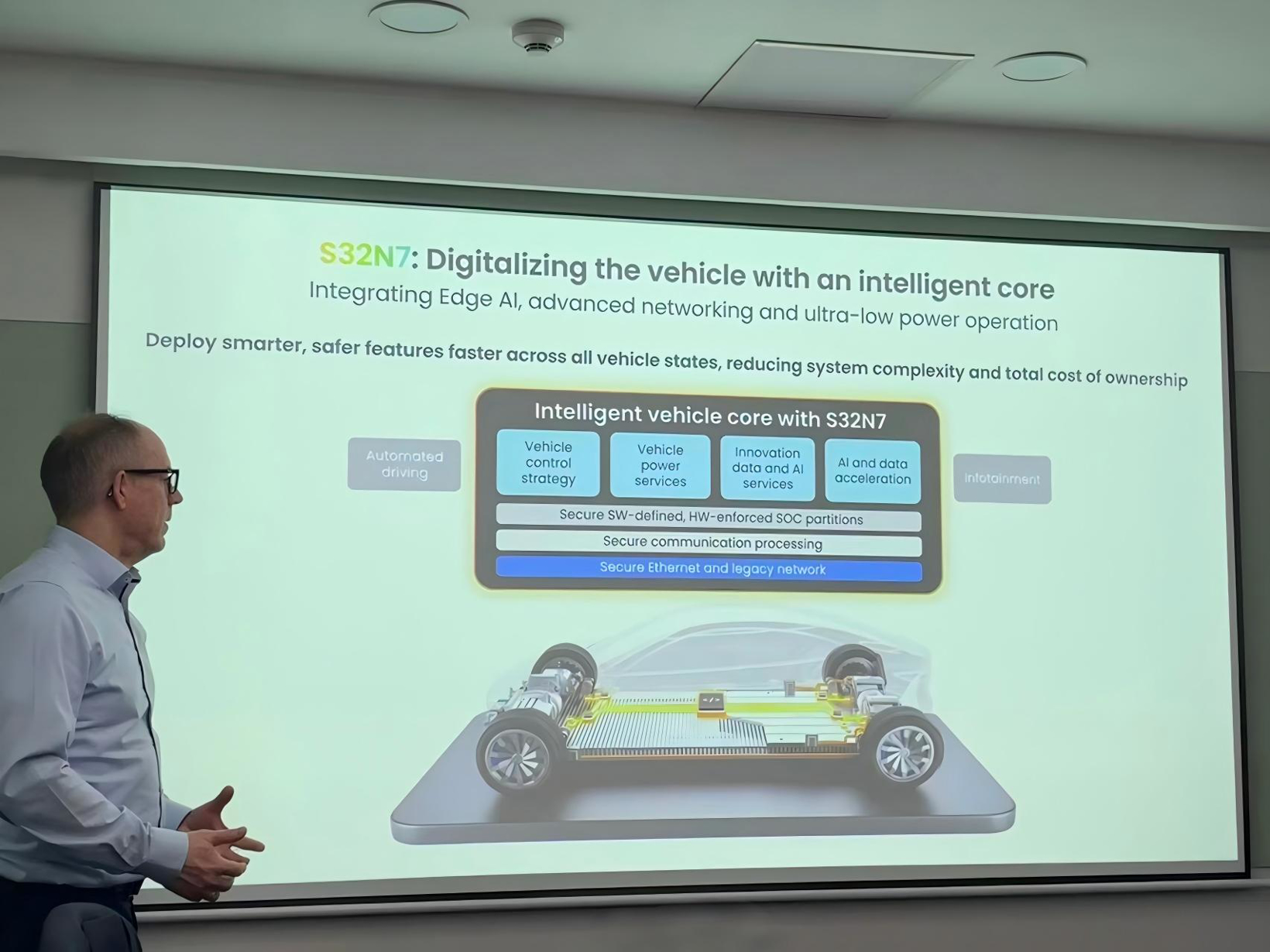

This is precisely the rationale behind NXP's launch of the S32N7 ultra-high-integration processor. Its core logic is to achieve centralized control of core vehicle functions, breaking down barriers between domains and ushering in a new era of automotive digitization.

Technically, the S32N7 is built on the same 5-nanometer technology platform as the S32N55. This advanced process node not only boosts performance but achieves extreme integration. It centralizes control of powertrain, vehicle dynamics, body, gateway, and safety domains on a single chip, consolidating software and data into a central hub while meeting high standards for functional safety and cybersecurity, significantly reducing system complexity.

The S32N7 packs 20 independent compute engines, including 8 Arm® Cortex®-A78AE application cores and 12 Arm® Cortex®-R52 real-time cores. Each core runs independently; if one core handles safety-critical tasks, it remains unaffected by others, truly achieving zero latency and high-level functional safety.

Jens Hinrichsen noted that core automotive functions like chassis, powertrain, and body are the vehicle's foundation—what makes a car a car. They demand extreme robustness, functional safety, and cybersecurity, alongside ultra-high real-time processing capabilities and zero latency performance.

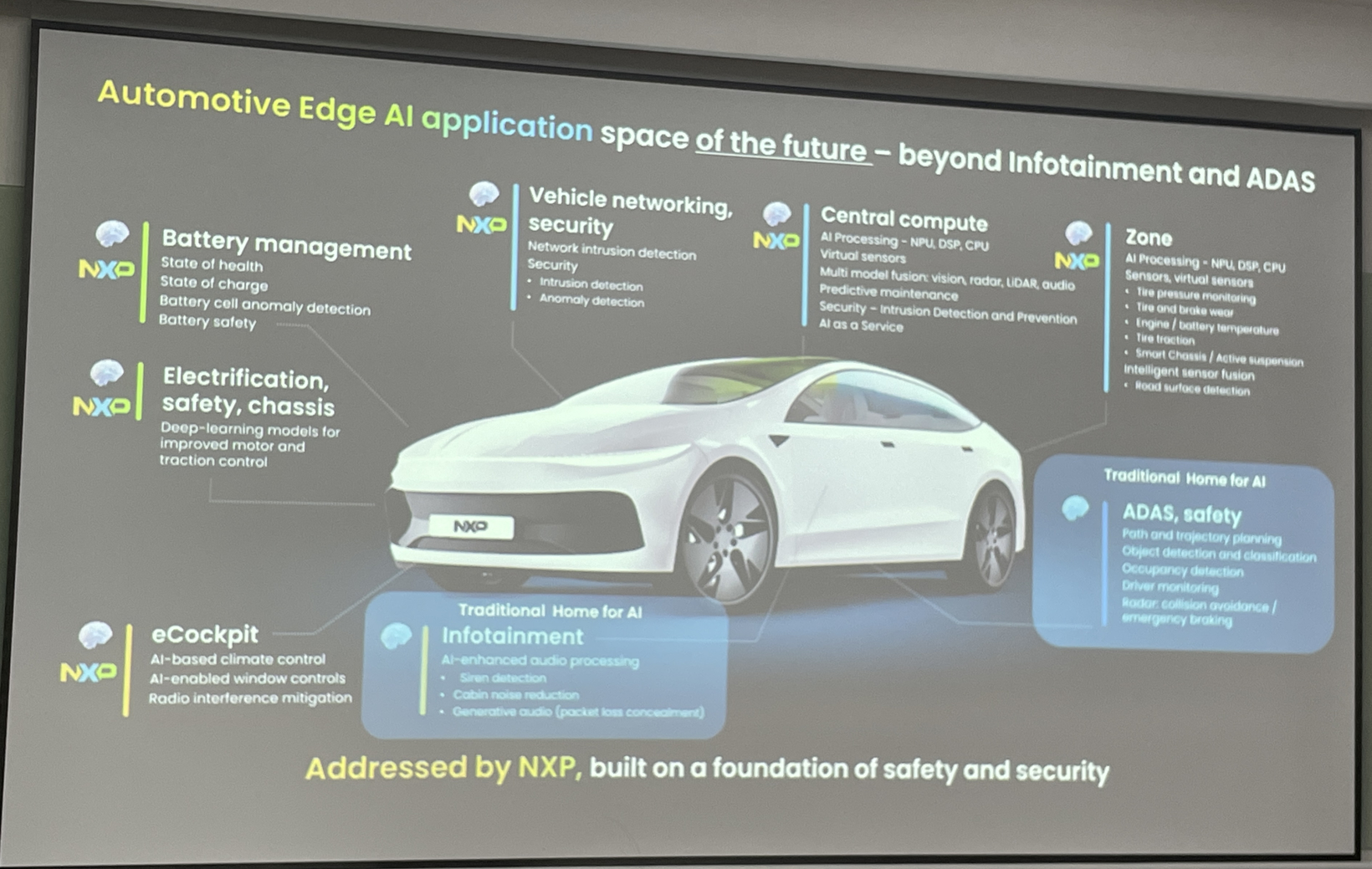

Meanwhile, the S32N7 shows promise in AI deployment. Its AI capabilities are specifically geared toward core vehicle functions. It features a built-in eIQ® Neutron NPU with a baseline computing power of about 2 TOPS. Jens Hinrichsen indicated that while this figure isn't staggering, it is sufficient to support core vehicle AI functions.

Specifically, it supports practical scenarios like battery anomaly detection, predictive maintenance, and intelligent energy management. For instance, AI algorithms can monitor battery cell thermal consumption in real-time to predict thermal runaway risks, or intelligently shut off unnecessary functions while driving—reducing energy consumption and extending range without the driver noticing.

Crucially, its PCI Express interface allows for external AI chips (such as four Kinara chips delivering 160 TOPS), reserving ample space for future AI expansion. This ensures upgrades to the latest AI chips are possible without redesigning the entire vehicle architecture.

For automakers, the S32N7's core value lies in tangible benefits. By eliminating dozens of hardware modules and optimizing wiring and electronics, it helps reduce Total Cost of Ownership (TCO) by up to 20%.

Jens Hinrichsen detailed the origin of this figure: "We compared the BOM costs of distributed versus centralized architectures—including the full chain of semiconductors, wiring harnesses, ECUs, software, and software licenses—ultimately concluding that the total cost of ownership can be reduced by about 20%."

He further emphasized that the biggest advantage in cost savings lies in architecture reusability: "This reusability supports software updates on existing hardware. Through OTA upgrades throughout the vehicle's lifecycle, manufacturers can continuously enjoy the TCO reduction benefits that reusability brings."

Additionally, the S32N7 supports hardware and software scalability across vehicle models and brands, helping automakers establish a foundational platform. This allows for the expansion of AI-driven innovations across the entire vehicle range and accelerates the implementation of software business models.

Ecosystem Synergy: The Critical Variable to Breaking Through Mass Application

The mass application of central computing chips is never a solo act by a single company; it requires the combined strength of Tier 1 suppliers, automakers, and chipmakers. Although the S32N7 has distinct technical advantages, moving from sample to mass production involves overcoming challenges like ecosystem adaptation, migration of existing customer ecosystems, and managing production timelines.

Bosch's early entry has become a significant breakthrough. As the first Tier 1 supplier to deploy the S32N7 in an integrated vehicle platform, Bosch has partnered deeply with NXP. Together, they developed reference designs, safety frameworks, hardware integration solutions, and expert empowerment plans to accelerate system deployment and reduce the integration workload for early adopters.

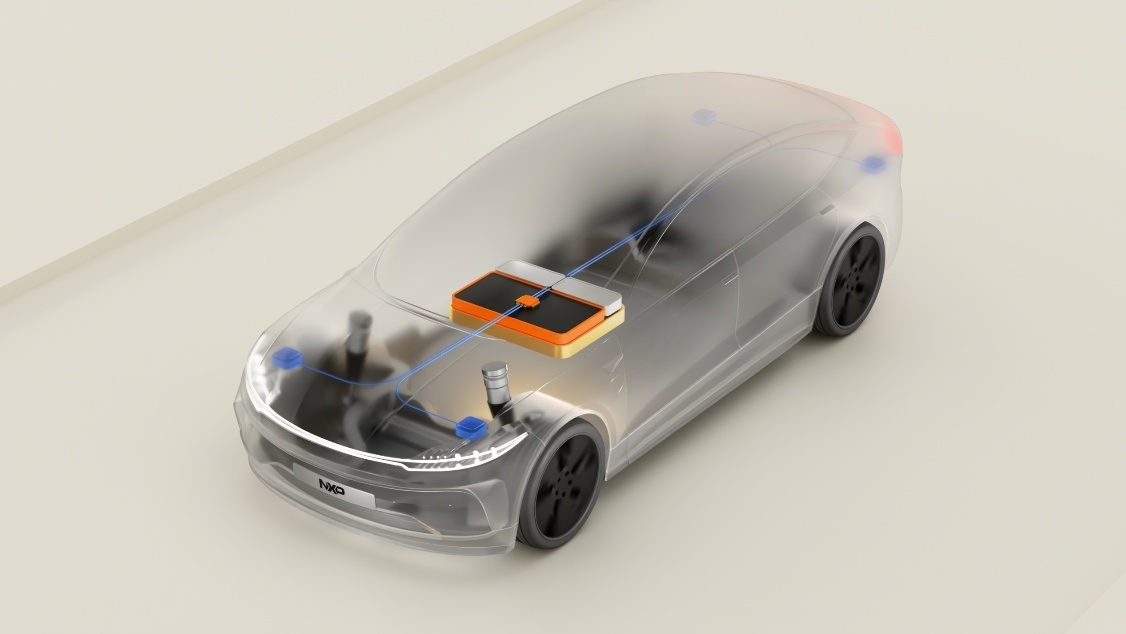

Image Source: NXP

Currently, Bosch is creating a vehicle architecture based on the S32N7 to build an industry demonstration platform, fully showcasing the chip's core advantages.

Furthermore, NXP has equipped the S32N7 with a complete software toolchain and middleware support, including MotionWise middleware from TTTech Auto, helping automakers quickly complete software adaptation and function development to shorten time-to-market.

The difficulty of migrating customers' existing ecosystems is a core challenge in the S32N7's market push. Automakers today have established mature control ecosystems in powertrain and chassis, where every component has its dedicated hardware and software system. Compatibility issues become a major roadblock during migration.

"The industry urgently needs to simplify vehicle sub-ecosystems. The complete architecture and software platform provided by the S32N7 help automakers gradually migrate edge node functions to the central computing unit," Jens Hinrichsen said. This process takes time, but the trend is irreversible—much like the integration experienced by the computer, server, and phone industries—only the automotive sector is more complex and requires a longer transition cycle.

Regarding production rhythm, Jens Hinrichsen revealed a general plan in an interview with Gasgoo: "We expect a streamlined version of the S32N7 to hit the market around late 2027 or early 2028, with the full version following shortly after."

Notably, NXP views the Chinese market as a critical battleground for the S32N7's mass application. Jens Hinrichsen told Gasgoo that Chinese automakers have shown very strong interest in the S32N7 and are the most active in landing AI applications.

Two core reasons drive this: First, competition in China's new energy vehicle market is fierce. Automakers need architecture upgrades to achieve differentiation. The S32N7's cross-model and cross-brand scalability helps them rapidly expand their product matrix and international business. Second, Chinese automakers are more aggressive in AI application; they need a reliable AI platform to deeply integrate AI functions into core vehicle operations.

Chain Reaction: How Architectural Change Reshapes the Industry Landscape

Every iteration of automotive E/E architecture triggers a deep reconstruction of the supply chain. From distributed ECUs to domain controllers and now to central computing, the industry is undergoing a full-chain transformation covering technical roadmaps, business models, and division of labor. The development of central computing chips will be the core catalyst of this change.

The design philosophy of the S32N7 fully reflects a judgment of the industry's long-term evolution. Jens Hinrichsen emphasized: "The S32N7 is not designed to serve just one generation of vehicles, but to reserve ample space for the long-term evolution of software-defined vehicles."

Its PCI Express interface allows for flexible AI expansion, enabling automakers to support upgrades from L2 to L3 autonomous driving without reconstructing the vehicle architecture. Meanwhile, continuous online AI functions remain stable even when ADAS or IVI processors are powered down.

This "scalable and upgradable" nature aligns perfectly with the core demands of software-defined vehicles. It allows automakers to continuously push new features via OTA on existing hardware, extending the vehicle's lifecycle value and making the product form of a "lifetime upgrade" car a reality.

The reconstruction of business models is breaking traditional industry boundaries. In the past, automakers' profit models relied heavily on hardware sales, with software functions mostly "one-time deliveries," making it difficult to generate recurring revenue after the vehicle was sold.

The advent of central computing architectures makes it possible for automakers to realize "paid software" by leveraging centralized computing power and full-vehicle data access to continuously push new features via OTA. This transition from "hardware sales" to "hardware + software + services" will not only reshape automakers' profit structures but also drive the formation of a new business model where "hardware is the foundation, software is the soul, and service is the wings," unlocking long-term revenue potential.

The division of labor within the supply chain is undergoing profound changes. For Tier 1 suppliers, a transformation into "system solution providers" is mandatory, requiring the integration of chips, software, and hardware resources to provide automakers with integrated solutions.

For automotive chip companies, the competitive focus has shifted from single performance metrics to a comprehensive contest of integration, real-time capability, functional safety, AI scalability, and ecosystem completeness. Technical barriers will rise even further.

Notably, the widespread adoption of central computing architectures will also accelerate the application of RISC-V architecture in the automotive sector.

Jens Hinrichsen revealed at the briefing: "Currently, the microcontrollers and microprocessors NXP offers customers use Arm® Cortex® cores, which is the optimal ecosystem choice available right now. However, in the backend operations invisible to consumers—including hidden cores like DSP—we are actually already using the RISC-V architecture."

He added: "We are vigorously promoting the improvement of the RISC-V ecosystem. When the RISC-V ecosystem is ready, we will provide relevant support to customers in a timely manner. Until then, NXP must guarantee customers stable and reliable Arm core products."

From a long-term industry perspective, the widespread adoption of central computing architecture is an inevitable choice for the automotive sector's transition toward electrification, intelligence, and connectivity. The emergence of chips like the S32N7 provides key technical support for this shift.

Although challenges like ecosystem adaptation and technical migration still require time to overcome, it is undeniable that the curtain on the era of central computing has risen. In the future, only those companies that can accurately grasp technological trends, build synergistic ecosystems, and respond quickly to market demands will seize the opportunity in this industrial reconstruction and lead the direction of industry development.